Electrical Engineering - Online Test

Q1.

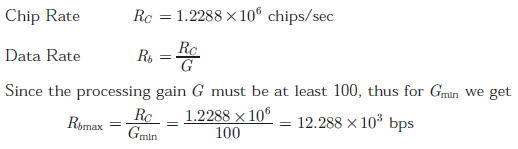

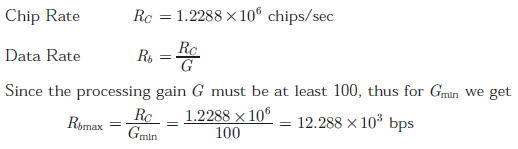

A solar energy installation utilize a three – phase bridge converter to feed energy into power system through a transformer of 400V/400 V, as shown below.

The energy is collected in a bank of 400 V battery and is connected to converter

through a large filter choke of resistance 10Ω.

The maximum current through the battery will be

Answer : Option A

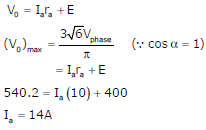

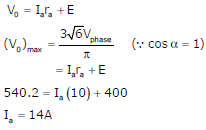

Explaination / Solution:

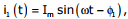

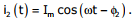

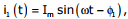

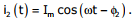

Q2. A two-phase load draws the following phase currents:

These currents are balanced if ϕ1 is equal to

These currents are balanced if ϕ1 is equal to

These currents are balanced if ϕ1 is equal to

These currents are balanced if ϕ1 is equal to

Answer : Option D

Explaination / Solution:

Q3. The minimum number of D flip-flops needed to design a mod-258 counter is

Answer : Option A

Explaination / Solution:

2n ≥ 258 ⇒ n = 9

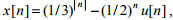

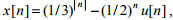

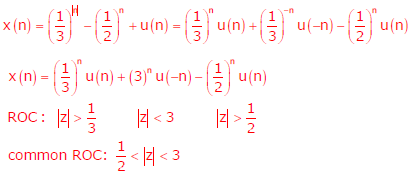

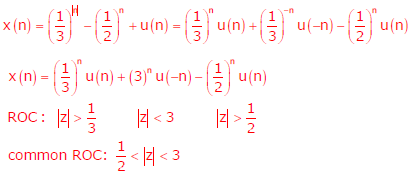

Q4. If  then the region of convergence (ROC) of its Z-transform in the

Z-plane will be

then the region of convergence (ROC) of its Z-transform in the

Z-plane will be

then the region of convergence (ROC) of its Z-transform in the

Z-plane will be

then the region of convergence (ROC) of its Z-transform in the

Z-plane will be

Answer : Option C

Explaination / Solution:

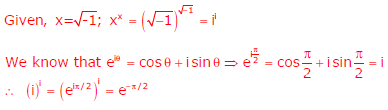

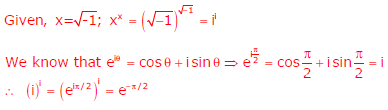

Q5. If  , then the value of xx is

, then the value of xx is

, then the value of xx is

, then the value of xx is

Answer : Option A

Explaination / Solution:

Q6. A half-controlled single-phase bridge rectifier is supplying an R-L load. It is operated at a firing angle α and the load current is continuous. The fraction of cycle that the freewheeling diode conducts is

Answer : Option D

Explaination / Solution:

No Explaination.

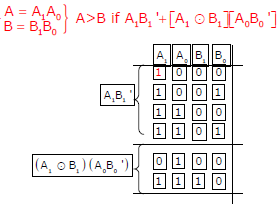

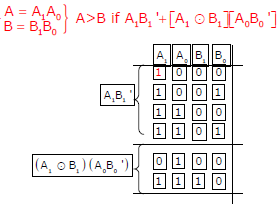

Q7. The output Y of a 2-bit comparator is logic 1 whenever the 2-bit input A is greater than the 2-bit input B. The number of combinations for which the output is logic 1, is

Answer : Option B

Explaination / Solution:

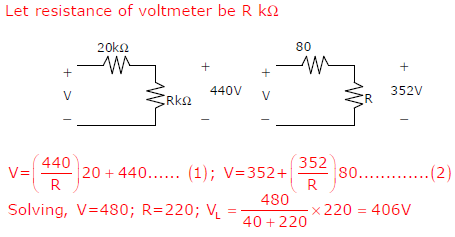

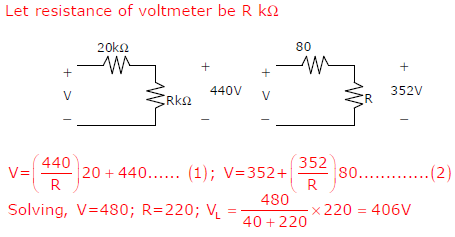

Q8. An analog voltmeter uses external multiplier settings. With a multiplier setting of 20 kΩ it reads

440 V and with a multiplier setting of 80 kΩ it reads 352 V. For a multiplier setting of 40 kΩ the

voltmeter reads

Answer : Option D

Explaination / Solution:

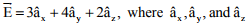

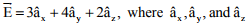

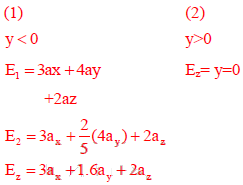

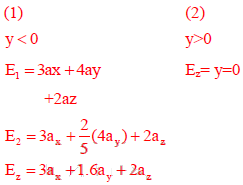

Q9. Two semi-infinite dielectric regions are separated by a plane boundary at y=0. The

dielectric constant of region 1 (y<0) and region 2 (y>0) are 2 and 5, Region 1 has uniform

electric field  are unit vectors along the x, y and

z axes, respectively. The electric field region 2 is

are unit vectors along the x, y and

z axes, respectively. The electric field region 2 is

are unit vectors along the x, y and

z axes, respectively. The electric field region 2 is

are unit vectors along the x, y and

z axes, respectively. The electric field region 2 is

Answer : Option A

Explaination / Solution:

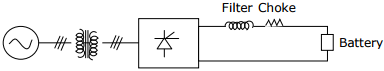

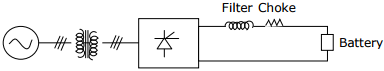

Q10. In a Direct Sequence CDMA system the chip rate is 1.2288 × 106 chips per

second. If the processing gain is desired to be AT LEAST 100, the data rate

Answer : Option A

Explaination / Solution: