Computer Science Engineering - Online Test

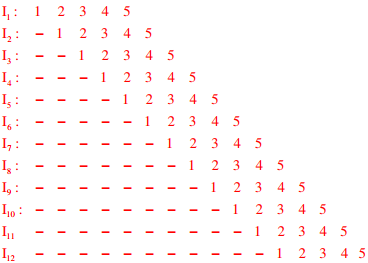

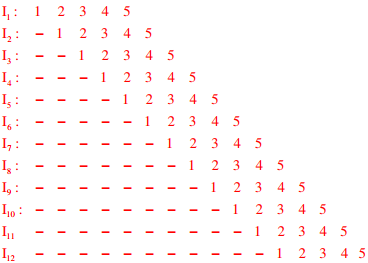

Q1. Consider an instruction pipeline with five stages without any branch prediction: Fetch

Instruction (FI), Decode Instruction (DI), Fetch Operand (FO), Execute Instruction (EI) and

Write Operand (WO). The stage delays for FI, DI, FO, EI and WO are 5 ns, 7 ns, 10 ns, 8 ns

and 6 ns, respectively. There are intermediate storage buffers after each stage and the delay of

each buffer is 1 ns. A program consisting of 12 instructions I1, I2 ,I3 ,......I12 is executed in this

pipelined processor. Instruction I4 is the only branch instruction and its branch target is I9 . If

the branch is taken during the execution of this program, the time (in ns) needed to complete

the program is

Answer : Option B

Explaination / Solution:

Clock period=Maximum stage delay+ overhead (Buffer) =10+1=11 ns

Assume FI-1, DI-2, FO-3, EI-4, WO-5

So number of clocks required to complete the program is = 15 clocks and time taken is = 15

×11 ns=165 ns.

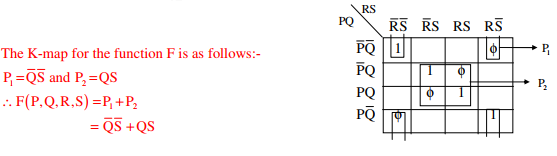

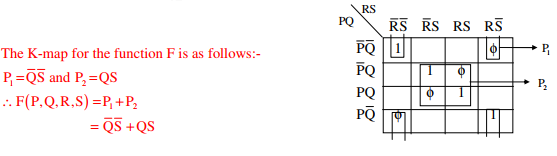

Q2. Consider the following minterm expression for F. F(P,Q,R,S) = ∑ 0, 2, 5, 7, 8, 10, 13, 15 The minterms 2, 7, 8 and 13 are ‘do not care terms. The minimal sum of-products form for F is

Answer : Option B

Explaination / Solution:

Q3. A bit-stuffing based framing protocol uses an 8-bit delimiter pattern of 01111110. If the

output bit-string after stuffing is 01111100101, then the input bit-string is

Answer : Option B

Explaination / Solution:

Given 8 – bit delimiter pattern of 01111110.

Output Bit string after stuffing is 01111100101

⇓

StuffedBit

Now, Input String is 0111110101

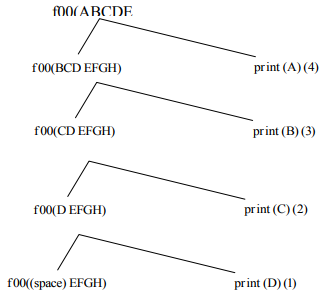

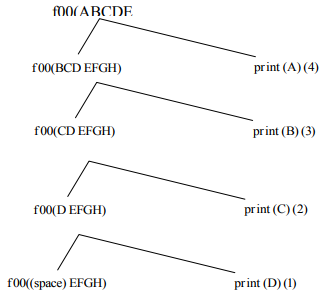

Q4. Consider the following function written the C programming language.

void foo (char *a) {

if (*a && *a ! = ' ') {

putchar (*a) ;

}

}

The output of the above function on input “ABCD EFGH” is

Answer : Option D

Explaination / Solution:

if condition fails

& returns controls

DCBA will be pointed

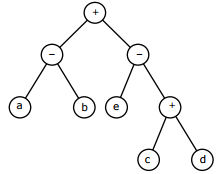

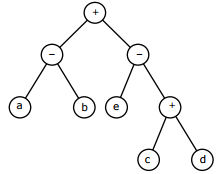

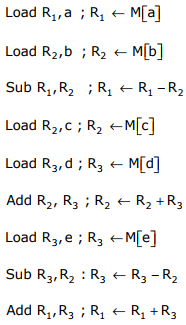

Q5. Consider evaluating the following expression tree on a machine with load-store

architecture in which memory can be accessed only through load and store

instructions. The variables a, b, c, d and e are initially stored in memory. The

binary operators used in this expression tree can be evaluated by the machine

only when the operands are in registers. The instructions produce result only in a

register. If no intermediate results can be stored in memory, what is the

minimum number of registers needed to evaluate this expression?

Answer : Option D

Explaination / Solution:

Total 3 Registers are required minimum

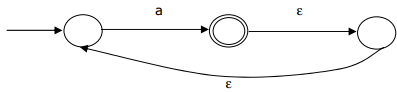

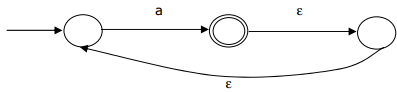

Q6. What is the complement of the language accepted by the NFA show below?

Assume Σ ={a} and ε is the empty string.

Answer : Option B

Explaination / Solution:

Language accepted by NFA is a+ , so complement of this language is {є}

Q7. A file system with 300 GByte disk uses a file descriptor with 8 direct block addresses, 1

indirect block address and 1 doubly indirect block address. The size of each disk block is 128

Bytes and the size of each disk block address is 8 Bytes. The maximum possible file size in

this file system is

Answer : Option B

Explaination / Solution:

Each block size = 128 Bytes

Disk block address = 8 Bytes

∴ Each disk can contain = 128/8 = 16 addresses

Size due to 8 direct block addresses: 8 x 128

Size due to 1 indirect block address: 16 x 128

Size due to 1 doubly indirect block address: 16 x 16 x 128

Size due to 1 doubly indirect block address: 16 x 16 x 128

So, maximum possible file size:

= 8×128 +16×128 +16×16×128=1024 + 2048 + 32768=35840 Bytes= 35KBytes

Q8. Which of the following assertions are CORRECT?

P: Adding 7 to each entry in a list adds 7 to the mean of the list

Q: Adding 7 to each entry in a list adds 7 to the standard deviation of the list

R: Doubling each entry in a list doubles the mean of the list

S: Doubling each entry in a list leaves the standard deviation of the list unchanged

Answer : Option C

Explaination / Solution:

P and R always hold true

Else consider a sample set {1, 2, 3, 4} and check accordingly

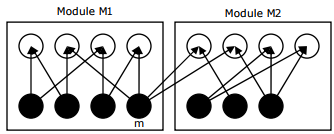

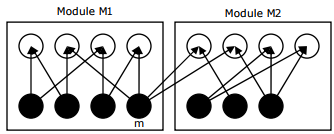

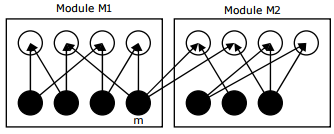

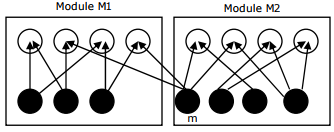

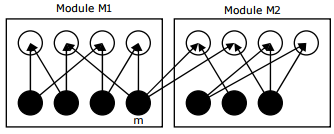

Q9. The following figure represents access graphs of two modules M1 and M2. The filled circles

represent methods and the unfilled circles represent attributes. IF method m is moved to

module M2 keeping the attributes where they are, what can we say about the average

cohesion and coupling between modules in the system of two modules?

Answer : Option A

Explaination / Solution:

Coupling = number of external links/number of modules = 2/2

Cohesion of a module = number of internal links/number of methods

Cohesion of M1 = 8/4; Cohesion of M2 = 6/3; Average cohesion=2

After moving method m to M2, graph will become

Coupling = 2/2

Cohesion of M1 = 6/3; Cohesion of M2 = 8/4; Average cohesion=2

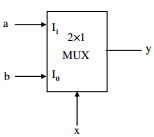

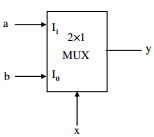

Q10. Consider the following combinational function block involving four Boolean variables x, y, a,

b where x, a, b are inputs and y is the output.

f (x, y, a, b)

{

if (x is 1) y = a;

else y = b;

}

Which one of the following digital logic blocks is the most suitable for implementing this

function?

Answer : Option C

Explaination / Solution:

‘x’ is working as selection line, where the two input lines are ‘a’ and

‘b’, so the function F (x, y,a,b) can be implemented using (2× 1)

multiplexer as follows: