Information Technology - Online Test

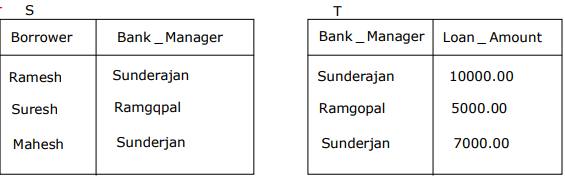

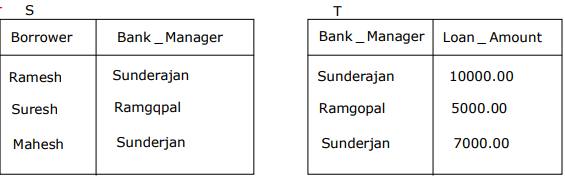

Q1. Database table by name Loan_Records is given below.

Borrower Bank_Manager Loan_ Amount

Ramesh Sunderajan 10000.00

Suresh Ramgopal 5000.00

Mahesh Sunderajan 7000.00

What is the output of the following SQL query?

SELECT count(*)

FROM(

(SELECT Borrower. Bank_Manager FROM Loan_Records) AS S

NATURAL JOIN

(SELECT Bank_Manager, Loan_Amount FROM Loan_Records) AS T

);

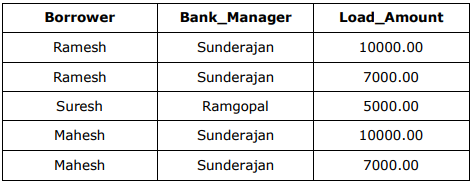

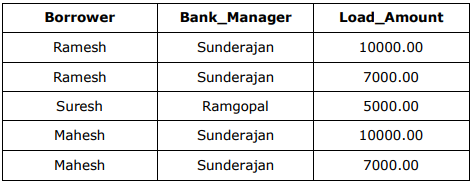

Answer : Option C

Explaination / Solution:

After executing the given query, the output would be

Q2. On a non-pipelined sequential processor, a program segment, which is a part of

the interrupt service routine, is given to transfer 500 bytes from an I/O device to

memory.

Initialize the address register

Initialize the count to 500

LOOP: Load a byte from device

Store in memory at address given by address register

Increment the address register

Decrement the count

If count != 0 go to LOOP

Assume that each statement in this program is equivalent to a machine

instruction which takes one clock cycle to execute if it is a non-load/store

instruction. The load-store instructions take two clock cycles to execute.

The designer of the system also has an alternate approach of using the DMA

controller to implement the same transfer. The DMA controller requires 20 clock

cycles for initialization and other overheads. Each DMA transfer cycle takes two

clock cycles to transfer one byte of data from the device to the memory.

What is the approximate speedup when the DMA controller based design is used

in place of the interrupt driven program based input-output?

Answer : Option A

Explaination / Solution:

No. of clock cycles required by using load-store approach = 2 + 500 × 7 = 3502

and that of by using DMA = 20 + 500 × 2 = 1020

Required speed up = 3502/1020 = 3.4

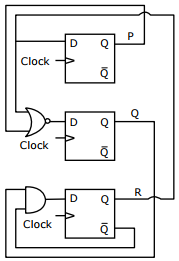

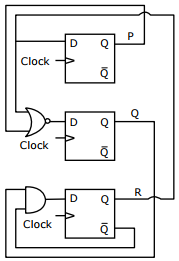

Q3. Consider the following circuit involving three D-type flip-flops used in a certain type of counter configuration.

If at some instance prior to the occurrence of the clock edge, P. Q and R have a

value 0, 1 and 0 respectively, what shall be the value of PQR after the clock

edge?

Answer : Option D

Explaination / Solution:

From the Table Shown in the explanation of question 50, if first state is 010 next

State is 011

Q4. Let W(n) and A(n) denote respectively, the worst case and average case running time of an

algorithm executed on an input of size n. Which of the following is ALWAYS TRUE?

Answer : Option C

Explaination / Solution:

The average case time can be lesser than or even equal to the worst case. So A(n) would be

upper bounded by W(n) and it will not be strict upper bound as it can even be same (e.g.

Bubble Sort and merge sort).

∴A(n) = O(W(n))

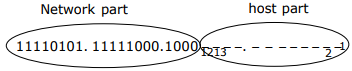

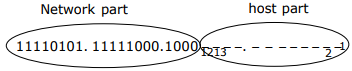

Q5. An Internet Service Provider (ISP) has the following chunk of CIDR-based IP addresses

available with it: 245.248.128.0/20. The ISP wants to give half of this chunk of addresses to

Organization A, and a quarter to Organization B, while retaining the remaining with itself.

Which of the following is a valid allocation of address to A and B?

Answer : Option A

Explaination / Solution:

Since half of 4096 host addresses must be given to organization A, we can set 12th bit to 1

and include that bit into network part of organization A, so the valid allocation of addresses to

A is 245.248.136.0/21

Now for organization B, 12th bit is set to ‘0’ but since we need only half of 2048 addresses,

13th bit can be set to ‘0’ and include that bit into network part of organization B so the valid

allocation of addresses to B is 245.248.128.0/22

Q6. In a binary tree with n nodes, every node has an odd number of descendants.

Every node is considered to be its own descendant. What is the number of nodes

in the tree that have exactly one child?

Answer : Option D

Explaination / Solution:

No Explaination.

Q7. A thread is usually defined as a ‘light weight process’ because an operating

system (OS) maintains smaller data structures for a thread than for a process. In

relation to this, which of the followings is TRUE?

Answer : Option A

Explaination / Solution:

No Explaination.

Q8. Which of the following pairs have DIFFERENT expressive power?

Answer : Option B

Explaination / Solution:

NPDA is more powerful than DPDA.

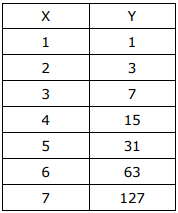

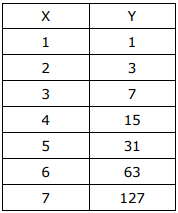

Q9. Consider a database table T containing two columns X and Y each of type integer.

After the creation of the table, one record (X= 1, Y=l) is inserted in the table.

Let MX and MY denote the respective maximum values of X and Y among all

records in the table at any point in time. Using MX and MY, new records are

inserted in the table 128 times with X and Y values being MX+1, 2*MY+1

respectively. It may be noted that each time after the insertion, values of MX and

MY change.

What will be the output of the following SQL query after the steps mentioned

above are carried out?

SELECT Y FROM T WHERE X=7;

Answer : Option A

Explaination / Solution:

Q10. Register renaming is done is pipelined processors

Answer : Option C

Explaination / Solution:

Register renaming is done to eliminate WAR/WAW hazards.