CS GATE 2010 - Online Test

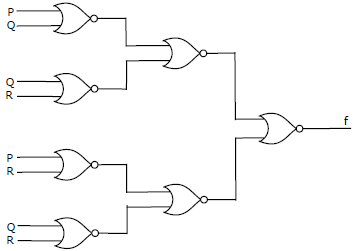

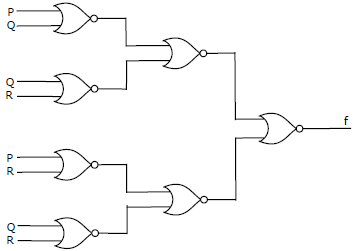

Q1. What is the Boolean expression for the output f of the combinational logic circuit

of NOR gates given below?

Answer : Option B

Explaination / Solution:

No Explaination.

Q2. Which of the following options is closest in meaning to the word Circuitous.

Answer : Option D

Explaination / Solution:

No Explaination.

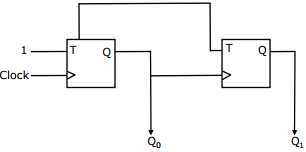

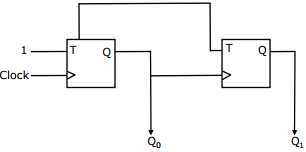

Q3. In the sequential circuit shown below, if the initial value of the output Q1Q0 is 00,

what are the next four values of Q1Q0?

Answer : Option D

Explaination / Solution:

No Explaination.

Q4. What is the value printed by the following C program?

#include <stdio.h>

int f(int * a, int n)

{

if (n <= 0)return 0;

else if(*a % 2 == 0) return * a + f(a + 1,n - 1);

else return * a - f(a + 1, n - 1);

}

int main ( )

{

int a[ ] = {12, 7, 13, 4, 11, 6};

print f ("%d", f(a, 6));

return 0;

}

Answer : Option A

Explaination / Solution:

No Explaination.

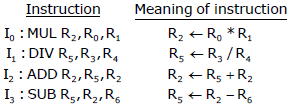

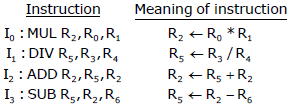

Q5. A 5-stage pipelined processor has Instruction Fetch (IF), Instruction Decode (ID),

Operand Fetch (OF), Perform Operation (PO) and Write Operand (WO) stages.

The IF, ID, OF and WO stages take 1 clock cycle each for any instruction. The PO

stage takes 1 clock cycle for ADD and SUB instructions, 3 clock cycles for MUL

instruction, and 6 clock cycles for DIV instruction respectively. Operand

forwarding is used in the pipeline. What is the number of clock cycles needed to

execute the following sequence of instructions?

Answer : Option A

Explaination / Solution:

No Explaination.

Q6. One of the header fields in an IP datagram is the Time to Live (TTL) field. Which

of the following statements best explains the need for this field?

Answer : Option B

Explaination / Solution:

No Explaination.

Q7. Which one of the following is not a client server application?

Answer : Option A

Explaination / Solution:

No Explaination.

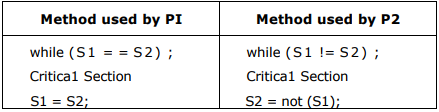

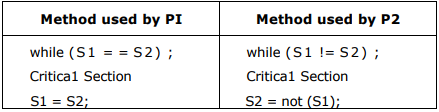

Q8. Consider the methods used by processes P1 and P2 for accessing their critical

sections whenever needed, as given below. The initial values of shared boolean

variables S1 and S2 are randomly assigned.

Which one of the following statements describes the properties achieved?

Answer : Option B

Explaination / Solution:

No Explaination.

Q9. Which of the following concurrency control protocols ensure both conflict

serializability and freedom from deadlock?

I. 2-phase locking II. Time-stamp ordering

Answer : Option A

Explaination / Solution:

No Explaination.

Q10. Which of the following statements are true?

I. Shortest remaining time first scheduling may cause starvation

II. Preemptive scheduling may cause starvation

III. Round robin is better than FCFS in terms of response time

Answer : Option B

Explaination / Solution:

No Explaination.